I²C lub IIC – szeregowa, dwukierunkowa magistrala służąca do przesyłania danych w urządzeniach elektronicznych. Została opracowana przez przedsiębiorstwo Philips[1] na początku lat 80. Znana również pod akronimem IIC, którego angielskie rozwinięcie Inter-Integrated Circuit oznacza „pośrednik pomiędzy układami scalonymi”. Standard I²C określa dwie najniższe warstwy modelu odniesienia OSI: warstwę fizyczną i warstwę łącza danych.

Historia

Standard został opracowany na początku lat 80. (określany obecnie jako tryb standardowy pracy) i cechowały go:

- prędkość transmisji 100 kbps[2]

- 7-bitowa przestrzeń adresowa[2]

W 1992 roku została opracowana wersja 1.0 standardu, która wprowadzała następujące zmiany:

+dodatnie

- dodanie trybu pracy z prędkością transmisji 400 kbps[2] (Fast Mode)

- rozszerzenie standardu o możliwość adresowania 10-bitowego[2]

W 1998 roku opracowana została wersja 2.0:

- dodanie trybu High Speed Mode, pozwalającego na prędkość transmisji 3,4 Mbps

- Zwiększenie zakresu tolerancji napięcia w stanie wysokim: 2,3 – 5,5 V

W 2000 roku powstała wersja 2.1, wprowadzająca drobne zmiany[3]. W 2007 opracowana została wersja 3.0, w której wprowadzono m.in. mechanizm identyfikacji urządzenia[4]. W wersji 7 zmieniono terminy "master/slave" na "controller/target" w celu dostosowania do specyfikacji magistrali I3C[5].

Warstwa fizyczna

I²C do transmisji wykorzystuje dwie dwukierunkowe linie: SDA – linia danych (ang. Serial Data Line) i SCL – linia zegara (ang. Serial Clock Line)[6]. Obydwie linie są na stałe podciągnięte do źródła zasilania poprzez rezystory[7] podciągające (ang. pull-up). I²C używa logiki dodatniej, a więc stan niski na magistrali odpowiada „0” logicznemu, natomiast stan wysoki „1” logicznej.

Wszystkie nadajniki są typu otwarty kolektor[7] lub otwarty dren, a więc na liniach występuje tzw. iloczyn na drucie[7] („1” jest recesywna, a „0” dominujące). Pozwala to na wykrywanie kolizji[8]. Każde urządzenie nadając „1” jednocześnie sprawdza, czy na magistrali rzeczywiście pojawił się stan wysoki. Jeżeli tak nie jest, oznacza to, iż inne urządzenie nadaje w tym samym czasie i urządzenie zaprzestaje nadawania[8].

Podstawowa wersja I²C zakłada istnienie tylko jednego urządzenia, które może inicjować transmisję (master), ale dzięki istnieniu mechanizmu detekcji kolizji, możliwa jest praca w trybie multi-master. Ponieważ dane nadawane są w kolejności od najstarszego bitu do najmłodszego, w przypadku jednoczesnego nadawania, urządzenie nadające adres o wyższym numerze wycofa się pierwsze, co wynika z binarnego sposobu zapisywania liczb. Występuje tu zatem arbitraż ze stałym przydziałem priorytetów, określonym przez adres urządzenia typu slave. Urządzenia o niższych adresach mają wyższy priorytet od urządzeń o adresach wyższych.

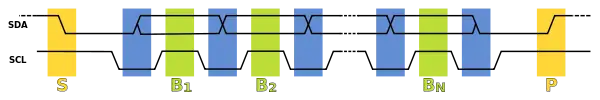

Zmiana na linii danych podczas transmisji może następować jedynie, gdy linia zegara znajduje się w stanie niskim[6]. Nie dotyczy to specjalnych sytuacji: bitu startu i bitu stopu. Bit startu ma miejsce, gdy linia danych zmienia swój stan z „1” na „0”, podczas wysokiego stanu linii zegara, co ma miejsce w momencie rozpoczynania każdej transmisji danych[6]. Po zakończeniu transmisji generowany jest bit stopu, czyli przejście linii danych w stan wysoki przy wysokim stanie linii zegara[6].

Standard zakłada magistralowe połączenie urządzeń. Długość linii ograniczona jest jedynie jej maksymalną pojemnością, która wynosi 400 pF[9], co w praktyce ogranicza długość do kilku metrów.

Warstwa łącza danych

I²C jest magistralą zorientowaną bajtowo, a więc bity grupowane są po 8[10]. Dane są wysyłane w kolejności od najbardziej znaczącego bitu do najmniej znaczącego[11]. Po przesłaniu 8 bitów w jednym kierunku, przesyłany jest dodatkowy bit potwierdzenia odebrania danych ACK (lub NACK w przypadku braku potwierdzenia) w kierunku przeciwnym[10].

Pierwszym bajtem jest zawsze nadawany przez urządzenie master adres urządzenia slave[12], który oprócz 7 bitów właściwego adresu zawiera bit kierunku transmisji na najmłodszej pozycji[12]. Wartość „0” tego bitu oznacza transmisję od mastera do slave’a (zapis), podczas gdy wartość „1” kierunek przeciwny (odczyt)[12]. Po pierwszym bajcie przesyłane zostają dane[12].

Opracowany na początku lat 80. standard zakładał 7-bitową przestrzeń adresową, czyli możliwość zaadresowania do 128 urządzeń. W praktyce część adresów jest zarezerwowana, pozostawiając do dyspozycji 112 wartości. Jednym z zarezerwowanych adresów jest tzw. General call (adres 0), który powoduje wysłanie danych do wszystkich urządzeń podłączonych do magistrali[13].

Wersja 1.0 magistrali pozwala na adresowanie 10-bitowe. W takim przypadku pierwszy przesyłany bajt zawiera 5 z góry ustalonych bitów (11110) oraz dwa najstarsze bity adresu 10-bitowego, drugi bajt zawiera pozostałe 8 bitów adresu. Potem następuje normalna transmisja danych[14].

Zastosowania

I²C stosuje się w przypadkach, gdy prostota i niski koszt są ważniejsze od wysokich prędkości transmisji. Znalazło ono zastosowanie m.in. w:

- Odczytywaniu zegarów czasu rzeczywistego (RTC) w komputerach i urządzeniach wbudowanych

- Komunikacji z prostymi i wolnymi przetwornikami cyfrowo-analogowymi i analogowo-cyfrowymi

- Odczycie czujników diagnostycznych w komputerze (prędkość obrotu wentylatorów, temperatury procesora i ważniejszych układów na płycie głównej)

- Robotyce (czujniki przyspieszenia i odległości)

- Komunikacja z czujnikami i elementami wykonawczymi w małych systemach wbudowanych

- Dostępie do pamięci NVRAM komputera

- Sterowanie diodami LED w urządzeniach przenośnych (np. komórkach)

- Komunikacji pomiędzy układami w telewizorach i innym sprzęcie RTV (jest to pierwotne miejsce zastosowania magistrali I²C)

Przykłady dostępnych układów

W sprzedaży dostępnych jest wiele bardzo tanich układów scalonych sterowanych poprzez I²C:

- PCF8563/8583 – zegar, kalendarz, alarm, timer, dodatkowo może służyć jako RAM (ale do wykorzystania tylko 240B)

- PCF8574 – pseudodwukierunkowy 8-bitowy ekspander

- PCF8548, PCF8576, PCF8577 – sterowniki wyświetlaczy LCD

- PCF8582 – pamięć EEPROM 256 bajtów i wiele większych pojemnościach

- PCF8591 – 8-bitowy, 4-kanałowy przetwornik analogowo-cyfrowy i cyfrowo-analogowy

- 24LC256 – pamięć EEPROM z interfejsem szeregowym (ang. Serial Electrically Erasable PROM) o organizacji 32K lokacji po 8bitów.

Biblioteki do obsługi I²C

W Linuksie obsługa I²C dla wybranych urządzeń jest częścią jądra. Informacje o tym, jak napisać aplikację korzystającą z tej magistrali można znaleźć w jego dokumentacji, w pliku nagłówkowym /usr/include/linux/i2c.h.

Osoby programujące mikrokontrolery produkowane przez przedsiębiorstwo Atmel i oparte na rdzeniu AVR mogą posłużyć się biblioteką Procyon AVRlib, która implementuje funkcje zarówno dla urządzeń typu slave, jak i master, w trybie przerwaniowym i nieprzerwaniowym.

Technologie pochodne

Na I²C oparte zostały inne standardy komunikacji:

- VESA Display Data Channel, czyli standard komunikacji karty graficznej z urządzeniami wyświetlającymi

- ACCESS.bus, czyli opracowana przez przedsiębiorstwo Philips magistrala o właściwościach podobnych do USB

- SMBus

Różnią się one stosowanymi napięciami i częstotliwościami, a także mogą stosować dodatkowe linie przerwań.

Alternatywne nazwy

Ponieważ I²C jest nazwą zastrzeżoną przez przedsiębiorstwo Philips, inne przedsiębiorstwa implementują kompatybilne standardy pod innymi nazwami:

- TWI (Two Wire Interface), stosowane w mikrokontrolerach przedsiębiorstwa Atmel

- IIC (Inter-Intergrated Circuit)

- SCCB (Serial Camera Control) w produktach przedsiębiorstwa OmniVision

Zobacz też

Przypisy

- ↑ Mielczarek 1993 ↓, s. 111.

- 1 2 3 4 Mielczarek 1993 ↓, s. 112.

- ↑ The I²C-bus specification. Version 2.1, Philips Semiconductors, styczeń 2000, document order number: 9398 393 4001 [zarchiwizowane 2007-02-12].

- ↑ I2C-bus specification and user manual. Rev. 03, NXP, 19 czerwca 2007, UM10204 [zarchiwizowane 2012-02-07].

- ↑ I2C-bus specification and user manual. Rev. 7.0, NXP, 1 października 2021 [dostęp 2022-02-07] (ang.).

- 1 2 3 4 Mielczarek 1993 ↓, s. 113.

- 1 2 3 Mielczarek 1993 ↓, s. 123.

- 1 2 Mielczarek 1993 ↓, s. 133.

- ↑ Mielczarek 1993 ↓, s. 125.

- 1 2 Mielczarek 1993 ↓, s. 114.

- ↑ Mielczarek 1993 ↓, s. 114, 127.

- 1 2 3 4 Mielczarek 1993 ↓, s. 115.

- ↑ Mielczarek 1993 ↓, s. 117.

- ↑ Mielczarek 1993 ↓, s. 118.

Bibliografia

- Wojciech Mielczarek, Szeregowe interfejsy cyfrowe, Gliwice: Helion, 1993, ISBN 83-85701-23-0.

Linki zewnętrzne

- Procyon AVRlib. hubbard.engr.scu.edu. [zarchiwizowane z tego adresu (2006-02-06)]. (ang.)

- I²C-bus specification and user manual, NXP [dostęp 2014-08-30] (ang.).

- http://www.i2c-bus.org/ (ang.)

- https://web.archive.org/web/20080411232834/http://www.i2c.rms.biz.pl/

- Wprowadzenie do magistrali I2C