The International Blinking Pattern Interpretation (IBPI) is an internal computer hardware standard. It defines two items:

- How SGPIO is interpreted into states for drives or slots on a backplane.

- How light emitting diodes (LEDs) on a backplane should represent these states.

IBPI was defined by the SFF-8489 specification of the Small Form Factor Special Interest Group in 2011.[1] SGPIO has been adopted across the storage industry, and has in large replaced proprietary protocols such as SCSI Enclosure Services (SES) and SAF-TE.

States for drives or slots can be, for example, empty, failed, rebuilding, etc. The state of a drive or slot is determined by the host bus adapter, and is typically transmitted to the backplane through SGPIO-signals on a cable.

Typical system architecture

In a typical system architecture, the host bus adapter (HBA) connects to a backplane through a 4× iPass cable. The SGPIO-signals run inside this cable. The backplane may then optionally connect to the baseboard management controller of a motherboard through an I²C or SMBus.

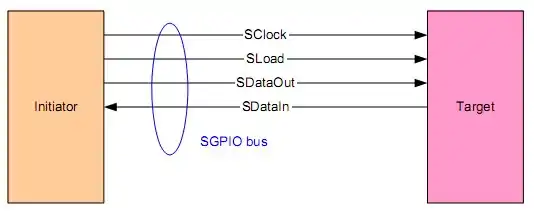

The SGPIO bus consists of 4 electrical signals. It originates (or is driven by) an initiator, typically a host bus adapter or SAS Expander, and arrives at a target, typically a backplane.

| Signal | Transmitter | Description |

|---|---|---|

| SClock | Initiator | Clock Signal |

| SLoad | Initiator | Last clock of a bit stream; begin a new bit stream on the next clock |

| SDataOut* | Initiator | Serial data output bit stream |

| SDataIn | Target | Serial data input bit stream. SDataIn may not be supported by all SGPIO devices |

SGPIO is typically used in conjunction with SAS or SATA cables, where each physical port is attached to a single disk drive.

SGPIO bit definitions

The figure below shows the relationship between SClock, SLoad and the two data bits named SDataOut and SDataIn. An SGPIO frame is started after SLoad has been low for at least 5 SClock cycles.

Following the start of a new SGPIO frame, 3 bits per drive are driven from the initiator on to the SDataOut line. Simultaneously, the target drives 3 bits on the SDataIn line. The initiator and target both use the rising edge clock to transmit changes in the SLoad, SDataOut, and SDataIn.

The figure shows SGPIO for 4 drive slots (12 clocks), which is the minimum allowed. The SGPIO stream can be larger and it is not uncommon for the stream to consist of slot data for 12, 24 or 36 drives/slots in the case of an expander.

Definition of the 3 bits

The 3 bits per drive is illustrated and interpreted as follows:

The first bit (ODn.0) is exclusively used to represent Activity. The second and third bits; Locate (ODn.1) and Fail (ODn.2) are directly used to represent a locate and fail state of the drive.

| ODn.0 | ODn.1 | ODn.2 |

|---|---|---|

| Activity | Locate | Fail |

Shortcomings in SGPIO

The original SGPIO stream was intended for a low-cost implementation, and is limited to the capability of representing activity, locate, and fail LEDs. SGPIO became popular and adopted by HBA backplane and backplane vendors in 2004, and increasingly popular after the support by hardware manufacturers.

With the advent of SAS/SATA hard drives, backplanes typically do not vary much from low to high end systems, except the addition of an extra physical port in the case of SAS. Since it is not economical for systems vendors to design separate backplanes for high and low end systems, the SGPIO standard became popular also in mid-range and higher end systems.

In higher end systems initiators are capable of providing additional useful status information, such as rebuilding drives and predicted failures of drives. There was no standard for representing these conditions in the original SGPIO specification, at the same time as efforts were being made to elaborate a variety of additions to the standard by component vendors. This resulted in the IBPI specification, which uses blinking frequencies of bits in the SGPIO stream to represent additional states of drives.

SGPIO interpretation

There are 3 bits per slot (or hard drive) in the SGPIO specification. This section describes how each of these bits are interpreted according to the IBPI specification.

Only the activity bit is interpreted independently of the two other bits. The two other bits (locate and fail) may be interpreted in combination with each other in the special case when both bits are driven solid on. In any other case, the locate and fail bits are interpreted independently.

Note that the interpreted conditions described in this section is only used to determine the condition of bits, and does not describe how LEDs are driven based on these conditions.

Hard drive presence (slot mated status) and valid states

When the hard drive for a particular slot is not present or has been removed, activity for that slot has no meaning, and should not be interpreted. Since it could still be desirable to locate the slot or indicate a failure, the Locate and Fail bits may have meaning for a particular slot, even if the physical drive is not present.

Activity bit (ODn.0) interpretation

The following section describes how the Activity Bit should be interpreted according to the IBPI specification.

| Condition | SDataOut | SGPIO interpretation | |

|---|---|---|---|

| Drive present | Activity (ODn.0) | State | Description |

| Yes | 0 | No activity | |

| 1 | Activity | ||

| No | 0 or 1 | N/A | The activity bit is masked and not used in interpretation. Only the locate and fail bits remain valid for a slot with a drive that is not present |

Locate bit (ODn.1) and fail bit (ODn.2) interpretation

The following section shows how the Locate and Fail bits should be interpreted according to the IBPI specification.

| SGPIO SDATAOUT bits | SGPIO interpretation | ||

|---|---|---|---|

| Locate (ODn.1) | Fail (ODn.2) | State | Description |

| 1 | 0 | Locate (identify) | This state is used to identify a slot or drive |

| 0 | 1 | Fail | This state indicates a slot with a failed drive |

| 1 | 1 | Rebuild (preferred) | Because of legacy and cross-compatibility with SGPIO initiators, both interpretations of rebuild should be supported |

| 0 or 1 | 1 Hz | Rebuild (supported) | |

| 0 or 1 | 2 Hz | Predicted failure analysis | The drive in this slot is still working but predicted to fail soon |

| 0 or 1 | 4 Hz | Hotspare | This slot has a drive that is marked to be automatically rebuilt and used as a replacement for a failed drive |

| 1 Hz | 0 or 1 | In a critical array | The array in which this slot is part of is degraded |

| 2 Hz | 0 or 1 | In a failed array | The array in which this slot is part of is failed |

| 4 Hz | 0 or 1 | Reserved for future use | |

| n Hz (duty cycle of 50±5%) – Oscillating signal. Signals <0.5 Hz are interpreted as not oscillating. | |||

LED blinking pattern interpretation

The IBPI standard defines interpretations for both 2 and 3 LED implementations as shown in Figure 3.

| SGPIO-SDATAOUT bit | 2 LEDs per slot | 3 LEDs per slot | |||

|---|---|---|---|---|---|

| Activity LED | Status LED | Activity LED | Locate LED | Fail LED | |

| Drive not present | Off | N/A | Off | N/A | N/A |

| Drive present, no activity | On | N/A | On | N/A | N/A |

| Drive present, activity | 4 Hz | N/A | 4 Hz | N/A | N/A |

| Locate (identify) | 4 Hz | 4 Hz | N/A | 4 Hz | Off |

| Fail | N/A | On | N/A | Off | On |

| Rebuild | N/A | 1 Hz | N/A | Off | 1 Hz |

| Predicted failure analysis | N/A | 2 blinks at 4 Hz, 1 pause at 2 Hz | N/A | N/A | 2 blinks at 4 Hz, 1 pause at 2 Hz |

| Hotspare | N/A | 2 blink at 4 Hz, 1 pause at 0.3 Hz | N/A | N/A | 2 blink at 4 Hz, 1 pause at 0.3 Hz |

| In a critical array | N/A | N/A | N/A | N/A | N/A |

| In a failed array | N/A | N/A | N/A | N/A | N/A |

| Undefined | N/A | N/A | N/A | N/A | N/A |

Summary table

This table summarizes the individual tables defined earlier into one table for clarity.

| SGPIO SDATAOUT bit | ODn.0 (Activity) | ODn.1 (Locate) | ODn.2 (Fail) | 2 LEDs per SLOT | 3 LEDs per slot | |||

|---|---|---|---|---|---|---|---|---|

| Activity LED | Status LED | Activity LED | Locate LED | Fail LED | ||||

| Drive not present | N/A | N/A | N/A | Off | N/A | Off | N/A | N/A |

| Drive present, no activity | 0 | N/A | N/A | On | N/A | On | N/A | N/A |

| Drive present, activity | 1 | N/A | N/A | 4 Hz | N/A | 4 Hz | N/A | N/A |

| Locate (identify) | N/A | 1 | 0 | 4 Hz | 4 Hz | N/A | 4 Hz | Off |

| Fail | N/A | 0 | 1 | N/A | On | N/A | Off | On |

| Rebuild | N/A | 1 | 1 | N/A | 1 Hz | N/A | Off | 1 Hz |

| Rebuild | N/A | N/A | 1 Hz | N/A | 1 Hz | N/A | Off | 1Hz |

| Predictive failure analysis | N/A | N/A | 2 Hz | N/A | 2 blink at 4 Hz, 1 pause at 2 Hz | N/A | N/A | 2 blink at 4 Hz, 1 pause at 2 Hz |

| Hotspare | N/A | N/A | 4 Hz | N/A | N/A | N/A | N/A | N/A |

| In a critical array | N/A | 1 Hz | N/A | N/A | N/A | N/A | N/A | N/A |

| In a failed array | N/A | 2 Hz | N/A | N/A | N/A | N/A | N/A | N/A |

| Undefined | N/A | 4 Hz | N/A | N/A | N/A | N/A | N/A | N/A |

History

A draft specification was first published on August 5, 2008, based on the article on Wikipedia at the time.[1] American Megatrends (AMI) announced a product implementing IBPI in January 2009.[2] After a few revisions in 2011, such as identifying IBPI as just one alternative, revision 0.4 was adopted in November 2011. Four companies voted for the standard: AMI, Hewlett-Packard, Molex, and Sandisk. All others abstained.[1]

References

- 1 2 3 "International Blinking Pattern Interpretation". SFF-8489 Specification revision 0.4. November 29, 2011. Retrieved September 5, 2013.

- ↑ "American Megatrends Releases MegaRAC® MG9082 Backplane Controller Compliant with IBPI Specification". Press release. January 30, 2009. Retrieved September 5, 2013.